芯片描述

芯片特点

| ○ | 2k×16-bit OTP ROM | ○ | 80×8-bit SRAM | |

| ○ | 8 级堆栈空间 | ○ | 可编程 WDT 预分频器 | |

| ○ | 可编程 WDT 时间(4.5ms、18ms),可控制 WDT 自由运行时间 | ○ | 带信号源选择、触发沿选择、溢出中断及预分频器的 8 位实时时钟/计数(TCC) | |

| ○ | 工作电压范围:2.1V~5.5V(-0℃~70℃)2.3V~5.5V(-40℃~85℃) | ○ |

工作频率范围(2 分频): 晶振模式:DC~16MHz,4.5V;DC~8MHz,3V; DC~4MHz,2.1V ERC 模式:DC~2MHz,2.1V IRC 模式:16MHz,4MHz,1MHz,8MHz |

|

| ○ | 系统高低频率的界限是 400kHz | ○ |

低功耗: 小于 1.5mA(4MHz/5V) 典型 15A (32kHz/3V) 典型 2A(睡眠模式,WDT 关闭,LVD 关闭) |

|

| ○ | 内置 RC 振荡电路:16MHz、1MHz、4MHz、8MHz | ○ | 低压复位:4.0V±0.3V、3.5V±0.3V、2.7V±0.3V @25℃ | |

| ○ | 低压检测:4.5±0.2V、4.0±0.2V、3.3±0.2V、2.2±0.2V @25℃ | ○ |

中断源: TCC 溢出中断 (IDLE 模式唤醒) 外部中断 (SLEEP/IDLE 模式唤醒) 比较器输出状态改变中断 (SLEEP/IDLE 模式唤醒) ADC 转换完成中断 (SLEEP /IDLE 模式唤醒) PWM1~3 周期中断 (IDLE 模式唤醒) PWM1~3 占空比中断 (IDLE 模式唤醒) P0 端口输入状态改变中断 (SLEEP /IDLE 模式唤醒) LVD 中断 (SLEEP /IDLE 模式唤醒) |

|

| ○ |

双向 I/O 口: 17 位可编程控制 pull-high I/OS(P1<7:0>,P0<7:0>,P20) 16 位可编程控制 open-drain I/OS(P1<7:0>,P0<7:0>) 17 位可编程控制 pull-low I/OS(P1<7:0>,P0<7:0>,P20) 14 位可编程控制 high-sink current I/OS (P1<7:0>,P0<7:6>,P0<4:1>) |

○ | 指令周期长度选择:2/4/8/16 个振荡时钟 | |

| ○ | 封装形式:DIP/SOP/SSOP20,DIP/SOP18 |

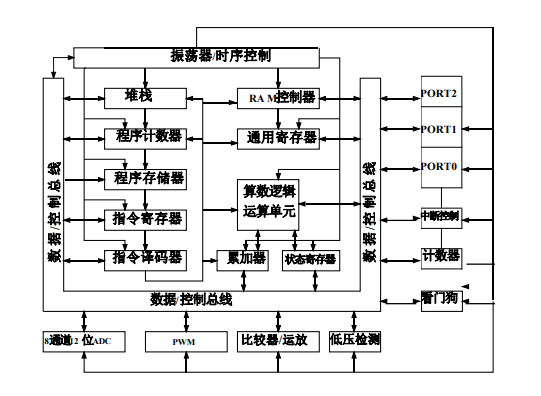

芯片框图